摘要:

等離子劃片是近年來興起的一項新型圓片劃片工藝。與傳統的刀片劃片、激光劃片等工藝不同,該工藝技術可以同步完成一張圓片上所有芯片的劃片,生產效率明顯提升,是對現有劃片工藝的一個顛覆。介紹了圓片劃片工藝的工作原理、技術特點及其優勢,并對其在解決圓片劃片應用中的典型問題和不足之處進行了討論。

1引言

圓片劃片是集成電路制造工藝中的一個重要環節,無論是傳統芯片封裝還是先進的圓片級封裝技術,劃片工序都是不可或缺的。對于傳統芯片封裝而言,圓片劃片是封裝過程的前段工序,而對于圓片級封裝,劃片往往成為封裝的最后步驟,一前一后都直接關系到封裝成品的最終可靠性。

圓片通常采用刀片切割進行芯片分離,即所謂的刀片劃片,刀片劃片工藝多采用金剛砂刀片作為劃片刀具,存在刀片磨損、切割過程中硅屑飛濺、崩邊、顆粒沾污等現象且無法避免。

隨著集成電路技術的不斷進步,芯片集成度在提升,圓片上的有效芯片尺寸也在不斷增加,伴隨的是劃片槽尺寸的進一步縮小,傳統的刀片劃片技術已經很難適應,激光劃片技術應運而生。激光劃片技術大致分為基于激光熔融的常規激光劃片、激光隱形切割(SD) 劃片和微水刀激光劃片 3 種主要形式。常規激光劃片技術主要用于 Low-K 工藝的圓片表面開槽,即采用高能激光將在 Low-K 工藝圓片表面的易碎鈍化層包括 PCM 圖形燒蝕 ;激光隱形切割技術則是利用特殊波長的激光打斷圓片劃片槽上的硅晶格,此過程不會在硅片有效圖形區中形成高溫,劃片后形成的劃痕寬度只有數微米;微水刀激光劃片結合常規激光劃片與水冷技術的特點,將高能量的激光束約束在一個狹小的水道中,劃片過程中同樣不會造成硅片中的熱損傷。

等離子劃片是近年來興起的一項全新的圓片劃片技術,它是采用等離子刻蝕技術在圓片劃片槽中形成窄小的蝕刻槽,使得芯片分離,與其他幾種劃片技術相比,可以一次性同步完成所有芯片的劃片,無需先后對所有劃片槽進行分步切割,其劃片速度與芯片大小無關,僅與圓片厚度相關,劃片效率明顯提升,是對現有劃片技術的一個顛覆。本文重點介紹這種先進的圓片劃片技術。

2 等離子劃片原理

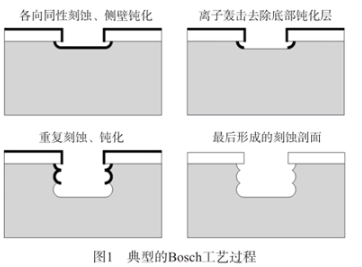

等 離 子 劃 片 技 術 源 于 ON Semiconductors 和Plasma-Therm 的專利授權,由 DISCO 公司開發成一種商用技術。等離子劃片的技術核心是等離子刻蝕工藝,即博世公司的深反應離子刻蝕工藝(DRIE),是一種微電子圓片制造過程中的硅材料干法腐蝕工藝,以博世公司開發的基于氟基氣體的具有高深寬比的硅刻蝕工藝最具代表性,即 Bosch 工藝,其典型工藝過程如圖 1 所示。Bosch 工藝中使用兩種含氟氣體 C 4 F 8 、SF 6 ,在第一套射頻電源的螺旋線圈產生感應耦合的電場作用下,刻蝕氣體輝光放電產生高密度等離子體,其中 C 4 F 8 生成聚合物,分別沉積在側壁和底部,形成抗腐蝕膜,以阻止側向刻蝕,該過程為鈍化過程;SF 6 為刻蝕氣體,SF 6 產生的等離子體首先對表面及底部沉積的聚合物進行轟擊,然后大流量的等離子體開始刻蝕硅。由于 SF 6 對于硅有較高的刻蝕選擇比,側壁的聚合物刻蝕速率較慢,所以形成一個深寬比較大(~ 20:1)的溝槽,此過程為刻蝕過程。在 Bosch 工藝中鈍化和刻蝕過程交替進行,一個完整的深反應刻蝕過程由數個鈍化 - 刻蝕循環組成。日本 Panasonic 公司開發了類似的等離子劃片技術,二者采用的是相同的深反應刻蝕工藝原理,同樣實現了商用化。

在圓片制造中,Bosch 工藝主要應用于 MEMS器件的結構形成以及 TSV 中的通孔制作。DISCO 公司聯合 ON Semiconductors 和 Plasma-Therm,巧妙利用了 DRIE 工藝原理,通過針對性的優化和改進,成功開發出一種圓片劃片工藝技術。

SF 6 對于圓片表面不同鈍化層的刻蝕速率是不同的,等離子刻蝕工藝也正是利用刻蝕氣體不同的刻蝕選擇比來實現正常刻蝕過程。所謂刻蝕選擇比 S R 是指同一刻蝕條件下,被刻蝕材料(即主體材料)的刻蝕速率與另一種材料(如光刻膠、PI 等屏蔽材料)的刻蝕速率之比,即:S R = E f / E r ,其中,E f 為被刻蝕材料的刻蝕速率,E r 為屏蔽材料的刻蝕速率。

SF 6 氣體對 Si 材料的刻蝕速率遠遠超過 SiO 2 、Si 3 N 4 和 PI,PI 刻蝕速率慢,即 Si 對 PI 的刻蝕選擇比較高,故通常選擇厚度大于 5 μm 的 PI 層來作為屏蔽層。光刻膠 PR 也是一種較好的屏蔽層。

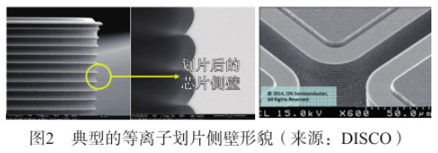

典型的等離子劃片側壁形貌如圖 2 所示。與標準的硅刻蝕工藝不同,等離子劃片僅僅是劃片槽中的局部硅材料區域進行刻蝕,也就是說適用于等離子劃片的圓片與傳統的圓片有所不同,前者需要在劃片槽的刻蝕區域暴露出需要刻蝕的硅本體材料,其他區域須被屏蔽層所覆蓋,否則其他區域會被同時刻蝕。

3 等離子劃片工藝流程

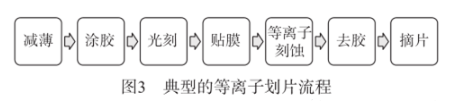

典型的等離子劃片工藝流程如圖 3 所示。

(1)減薄

按照工藝要求,將圓片減薄至設計厚度。通常情況下,減薄屬于劃片上工序。在等離子劃片中,減薄成為工序的一部分,目的是降低等離子刻蝕過程中產生的熱量。

(2)涂膠

在圓片表面涂覆光刻膠,通常采用 PI 作為刻蝕屏蔽層。所用設備為前道圓片制造中的標準涂膠設備及工藝。

(3)光刻

按照圓片厚度計算劃片槽刻蝕寬度,在劃片槽中光刻出所需圖形。通常按照圓片厚度與刻蝕寬度比小于 20:1 的原則選擇劃片槽刻蝕寬度。

(4)貼膜

按照不同的劃片方向(正面劃片或背面劃片),在圓片背面或正面貼上劃片膜(包括環框)。

(5)等離子刻蝕

對圓片正面或背面進行等離子刻蝕。以硅圓片為例,通常采用 C 4 F 8 、SF 6 兩種刻蝕氣體交替使用,其中C 4 F 8 用以鈍化,SF 6 用以刻蝕。去膠等離子刻蝕后,采用去膠機去除多余的光刻膠。

(6)摘片

最后摘取劃開的芯片,完成整個等離子劃片過程。

4 等離子劃片的優勢

等離子劃片本質上屬于一種化學反應,被刻蝕的硅材料與刻蝕氣體發生反應,其反應生成物形成氣體而被真空清除,因此與傳統的刀片劃片工藝和激光劃片工藝相比是一種清潔的劃片工藝,其主要優勢包括:

(1)超強的芯片強度

等離子劃片過程中隨著刻蝕氣體的持續轟擊作用,雖然圓片本身會發熱,但經過合理的冷卻裝置,實際圓片發熱遠低于激光劃片時由于硅材料的加熱氣化所產生的熱量,也沒有刀片劃片時高速切割過程中引入的機械應力,因此,采用等離子劃片獲得的芯片不存在崩邊、裂紋等常規劃片工藝中存在的常見問題,芯片強度明顯改善。

(2)超高的劃片速度

與傳統的刀片劃片、激光劃片工藝不同,等離子劃片過程中一張圓片所有劃片槽被同時刻蝕,圓片刻蝕速度與圓片厚度相關而與芯片大小無關,借助于等離子刻蝕氣體的高刻蝕選擇比,刻蝕速率可以達到每分鐘幾十微米,同樣厚度圓片的劃片速度是刀片劃片速度的 4 倍以上。

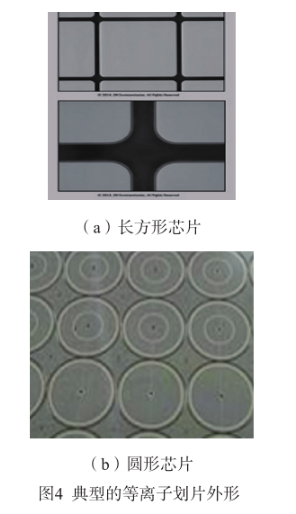

(3)可切割各種形狀芯片

得益于對硅材料的高選擇性刻蝕特性,等離子劃片可以實現任意形狀的芯片劃片,僅僅需要根據所要劃片的形狀在劃片槽中暴露出適當寬度的硅區域。相比之下,常規刀片劃片、激光劃片等工藝只能對排列規則、方形尺寸的芯片進行切割。

此外,等離子劃片后芯片角部通常為圓形,而不是常規劃片的直角,因而可以大大降低芯片崩邊、崩角現象。圖 4 為典型的等離子劃片外形,其中包括一些特殊器件如呈現圓形的 MEMS,而這種圓形芯片采用常規劃片工藝是很難實現的。

(4)可適應多種圓片材料

采用不同的刻蝕氣體可適應不同圓片材料的刻蝕,如含氟氣體 SF 6 等可適合于硅圓片的劃片,而選用含氯氣體如 HCl 以及其他氣體組合可用于 SiC、GaN 圓片的劃片。

當然等離子刻蝕并非適用于各種材料的劃片,如采用藍寶石基底材料的 LED 圓片就很難采用等離子劃片工藝,這是因為藍寶石的成分為 Al 2 O 3 ,Al 2 O 3 中的Al-O化學鍵極其牢固,常見的等離子很難打破Al-O鍵。

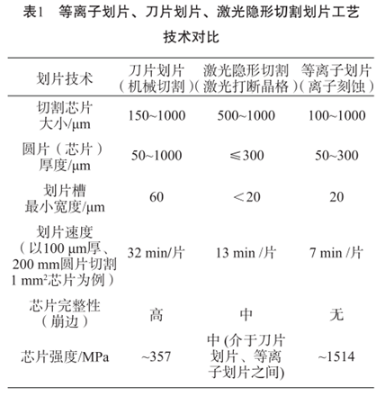

表 1 從芯片尺寸、劃片效率、芯片完整性及強度等方面對等離子劃片、刀片劃片、激光隱形切割劃片工藝技術進行了比較。

可以看出,等離子劃片技術在劃片效率、芯片完整性及芯片強度等方面具有明顯優勢。劃片速度約是激光隱形切割速度的 2.5 倍,比常規刀片劃片速度快3.5 倍 ;采用等離子劃片,芯片完整性更佳,崩邊問題可以規避 ;而采用等離子劃片后的芯片強度大約是

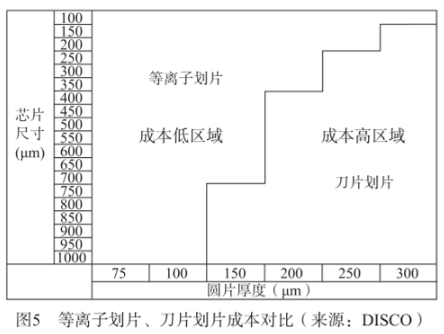

采用常規刀片劃片后芯片強度的 4.2 倍。DISCO 公司對等離子劃片、刀片劃片的生產成本進行了一個統計比較,見圖 5。可以看出圓片厚度小于 100 μm、劃片后芯片尺寸小于 100 μm×100 μm時,采用等離子劃片成本上有優勢。

5 工程應用及其推廣成本

從等離子劃片工藝原理可以看出,這是一種有別于常規劃片工藝的新型劃片工藝。該工藝技術充分利用了先進的半導體制造技術,前道工藝完美應用在了后道封裝工藝中。由于與主流的半導體制造技術兼容,等離子劃片工藝可以應用于目前市場上主流半導體圓片的切割。如硅圓片、鍺圓片、氮化鎵圓片、砷化鎵圓片等均可以采用等離子劃片工藝,劃片尺寸涵蓋76~300 mm直徑范圍。產品類型包括功率器件、RFID、LED、紅外傳感器、MEMS、通用 CMOS 器件等。

由于等離子劃片系一次性完成整張圓片的刻蝕,劃片速度僅與圓片厚度相關,故具有傳統劃片工藝連續劃片所無法比擬的劃片速度,尤其適合于尺寸小、厚度薄、芯片數量多的圓片劃片,從表 1、圖 5可以看出,100 μm 厚、200 mm 圓片切割 1 mm 2 芯片采用等離子劃片,生產效率是刀片劃片的 4 倍以上,同時成本優勢更加明顯。當圓片厚度減薄至 50 μm時,傳統的刀片劃片會面臨碎片等風險,只能借助復雜的 DBG 工藝加以規避,而采用等離子劃片工藝就可以輕松快速完成劃片,且不會造成碎片等異常,在保證成品率的同時,芯片強度得以提升(大約是采用刀片劃片的 4 倍)。

傳統劃片工藝在處理多項目圓片(MPW)時通常會面臨一些困難,特別是針對由多個尺寸不規則芯片的 MPW,劃片過程會變得非常復雜。若是只需要在整張圓片上進行切割,通常必須做出一些取舍,即只能保留一些指定的目標芯片,而部分或多個其他芯片必須做出犧牲。倘若要求將圓片中的所有芯片全部保留的話,則必須首先將一張圓片先切割成多個具有芯片組合的小塊(block),然后將這些 block 轉移至另外一張劃片膜中,這些 block 必須按照較高的放置精度排列,然后再進行第二次切割而分成更小的block。重復上述操作,直到所有的芯片被一一切割分離。如果 block 放置精度不滿足劃片要求,則只能有一個或少量幾個 block 被轉移至新的劃片膜中,切割效率很低,同時切割質量也難以保證。相比之下,等離子劃片技術無需如此復雜的流程,只要在所需要劃片的 MPW 中預留了劃片區,可以一次性完成所有芯片的切割,這也是傳統劃片技術無法比擬的絕對優勢。因此等離子劃片技術在 MPW 的劃片中有很好的應用前景。

在一些特殊的應用中,對于如 MEMS、Image sensor 等對顆粒物敏感的芯片,等離子劃片作為一種清潔、劃片過程無灰塵產生的潔凈劃片工藝,更是有著得天獨厚的優勢。對于 RFID 等劃片槽僅有 30~40 μm的微小尺寸器件,等離子劃片可以規避激光隱形切割中后擴片引入的微裂紋隱患,劃片成品率更高,成本優勢尤其明顯。

采用等離子劃片還可以避免刀片劃片工藝中劃片槽 PCM 圖形中的金屬條卷曲、脫落現象,可完全滿足高可靠應用中芯片鏡檢要求。

此外,在 2.5D、3D 集成封裝中,如有機基板、陶瓷基板的異質堆疊,不同 TCE 材料會引入應力,超薄芯片邊緣切割缺陷對此類產品的抗溫變能力以及封裝可靠性有影響,等離子劃片能較好地解決圓片切割引起的芯片邊緣缺陷問題。

目前該技術為日本 DISCO、Panasonic 及美國幾家公司擁有,其設備造價較高,加上需要額外的涂膠、光刻、去膠等專用設備,對于傳統的封裝線而言,前期投入較大,市場普及率不高,遠不及傳統的刀片劃片、激光劃片技術那樣被業界廣泛應用。雖然等離子劃片在劃片速度上較之刀片劃片、激光劃片有明顯的優勢,但如果將涂膠、光刻、去膠等工序計算在內,僅劃片速度的優勢將不復存在。前期投入大、需要相應的輔助工序,帶來較高的推廣成本,這些正是等離子劃片工藝應用中的最大不足之處。

6 結束語

等離子劃片技術是繼激光隱形切割技術之后的又一種先進劃片工藝技術,借鑒了半導體圓片制造中先進的干法刻蝕技術,通過一次性同步刻蝕在整張圓片中形成所有劃道,若僅考慮切割速率,是常規刀片劃片速率的 4 倍以上,對小尺寸芯片劃片生產效率的提升尤其明顯。通過獲得的更加圓滑的切割邊緣,在保證芯片完整性的同時還改善了芯片的機械強度,對于超薄芯片而言,可靠性及成品率優勢更明顯,是一種有潛力的劃片工藝技術。

隨著我國半導體制造設備的快速發展,干法刻蝕技術及裝備已經取得了很大的進步,目前國內等離子劃片機擁有量較低,倘若現階段充分利用這些等離子刻蝕機以及相關光刻設備資源,在等離子劃片技術及裝備上加大研發投入,應該有可能快速開發出我國自有品牌的等離子劃片系統,并可能占有市場,從而提升我國半導體制造設備的國產化水平及進程。