微電子制造和組件組裝是任何射頻產品生產鏈的關鍵步驟,因為它決定了產品的上市時間以及可以在有限的產品開發時間內進行重新設計周期的次數。 微電子制造是具有挑戰性的,因為制造的組件的小尺寸和它可以包括的特性,使得微電子制造容易受到環境,熱和電氣條件的影響。 了解這些挑戰和許多其他挑戰,導致微電子工藝工程作為一門獨立的學科出現,以應對這一領域的挑戰和迅速進步。

從CAD設計開始,最終以工作器件結束,需要遵循許多制造步驟和程序。 對于高產量和高直通率的目標,這些步驟需要徹底驗證,以提供一致的結果,從而可以鎖定這一特定器件的工藝過程。 工藝實驗可以包括材料選擇的幾個試驗,材料層的生長方法,層對層的對齊方法,以及材料圖案化方法。從一個制造商到另一個制造商, 每一個都可以是不同的,為任何人創造了大量的空間來發明新的工藝制成技術。 為了應對微電子制造的復雜性,具有不同背景的個人(例如物理、化學、電氣、機械工程和材料科學)和最新技術和設備的培訓技能通常協同參與工作,以使這一工藝取得成功。

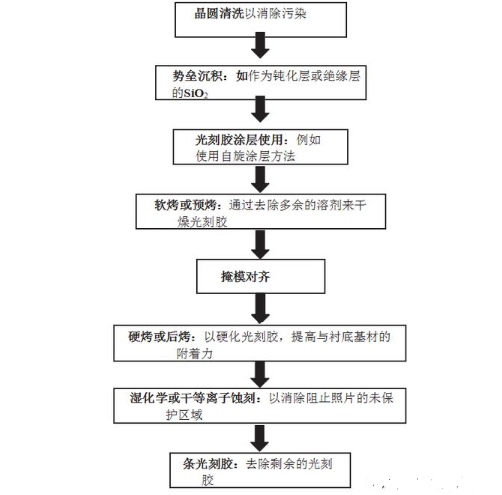

光刻(Photolithography fabrication)是通過光波將圖案從版圖或掩模轉移到半導體晶圓表面的工藝。 圖案的轉移機制首先使用一種光敏聚合物材料,稱為光刻膠圖案,其形狀定義在掩模上。 一旦圖案從掩模轉移到光刻膠,然后使用干法或濕法蝕刻方法將圖案從光刻膠轉移到晶圓的表面。 這個工藝本身由幾個步驟組成,需要建立幾個工具。 圖1所示的圖表概述了基本的光刻步驟,并簡要地解釋了每一步。

晶圓清洗通常是通過一套標準的步驟來進行的,并從將晶圓運行到溶劑中以清潔晶圓表面可能存在的顆粒和有機殘留物開始的:

圖1、 光刻工藝流程中涉及的基本步驟

接下來,晶片被徹底浸泡在去離子水(DI, deionized water)中,以去除任何剩余的溶劑,然后再進行RCA清潔。 該RCA清潔氧化晶圓提供一層薄的氧化物保護層到晶圓表面。 然后將晶圓浸泡在氫氟酸(HF,hydrofluoric acid)中,以去除晶圓表面的氧化層。 最后,晶圓被DI沖洗,然后用氮氣吹干。

薄膜材料的沉積通常采用化學氣相沉積(CVD, chemical vapor deposition)或物理氣相沉積(PVD,physical vapor deposition)。 作為一個概念,這兩種涂層工藝的應用都非常廣泛。 半導體制造商通常采用更具體的衍生技術。 PVD使用純源材料,通過蒸發氣化。 PVD熱供應是通過應用大功率電或激光燒蝕來完成的。 然后,蒸發材料將通過真空擴散到基片襯底表面,以產生所需的薄膜。 然而,CVD不需要純源材料,但該材料與揮發性前體混合作為材料載體。 然后,在一定溫度下,通過氣體輸送系統將涂層材料注入包圍襯底基片的反應室。 然后,蒸氣物質與底物反應并最終沉積在其上。 在這個階段,前驅體材料分解并離開沉積在襯底中的材料。 CVD工藝比PVD工藝需要更高的溫度。 根據應用的不同,因為幾個工藝制成方面的因素,如工藝復雜性、所需的薄膜厚度、原材料的可用性和成本原因,一種方法可能比另一種方法更好。 為此,在清洗晶圓后,屏障或鈍化層,如二氧化硅(SiO)2 通常沉積在晶圓的表面。

然后,利用標準自旋涂層技術將光刻膠層應用于晶圓的表面,通過每分鐘幾千輪(RPM)高速旋轉的晶圓基板產生離心力,能夠均勻地將光刻膠層分布在晶圓表面。 根據對外加光的反應,光刻膠可分為正抗蝕劑或負抗蝕劑。 在正抗蝕劑中,暴露在外加光下的抗蝕劑是可溶解的部分,因此可以通過光刻膠顯影液去除,而未暴露的抗蝕劑部分仍然不溶。 負光刻膠的作用方式與正抗蝕劑相反。 在這兩者之間,正抗蝕劑變得更加流行,因為它們為小幾何特征提供了相對更好的過程可控性。

其次,軟烘焙被用來去除所有溶劑后,光刻膠涂層工藝,在那里光刻膠變得光敏,因此軟烘焙是決定光成像質量的關鍵步驟。

在應用第一個光掩模后,每個后續掩模必須與前一個掩模對齊,以便能夠準確地將圖案轉移到晶圓表面。 掩模對準是使用掩模和晶圓上的對準標記來在光暴露前登記圖案。 一旦掩模對齊,光刻膠就會通過具有高強度光源的圖案掩模曝光,從而形成預期的圖案。

其次,在光刻過程中,硬烘焙步驟是必要的,以硬化所開發的光刻膠,并提高與晶片表面的附著力。

硬烤可能是不必須的工藝,而軟烘焙是需要的,如在金屬提升模式。

然后將不需要的光刻膠材料和殘留物蝕刻掉,從而在晶圓表面形成圖案。 模式轉移到晶圓表面可以使用三種方法之一:減法轉移(刻蝕)、添加劑轉移(選擇性沉積)和雜質摻雜(離子注入)。 減法采用濕化學或干等離子體刻蝕,這是最常用的模式轉移方法。 然而,干式蝕刻對濕式蝕刻提供了相對更多的輪廓控制。

要在掩模上印刷和圖案化小特征,需要根據方程(1)來使用波長較短的光源:

方程(1)

上式中R是分辨率,NA是確定光源可以發出光的角度范圍的孔徑數值,而λ是施加光的波長。

襯底基板是基本的建筑結構,用于提供機械支持和電氣連接到在幾乎任何射頻電路中的電子元件中。 在決策過程中,在為特定應用選擇合適的襯底技術時,除了制造成本和與特定制造技術的兼容性外,還必須考慮電氣、機械、化學和熱參數等幾種材料性能。 無論基板是共燒陶瓷(例如氧化鋁)、PCB(例如FR4)或半導體基板,事先了解材料性能對于了解基板和導體的不同性能是如何影響到特定設計的性能是至關重要的。

共燒陶瓷基板在介電材料純度和許多其他性能方面有著廣泛的品種。 陶瓷基板適用于高容量生產,可用于高微波頻率(高達50G Hz~),這取決于導體和介電材料在損耗方面的選擇。 共燒陶瓷可用于高密度射頻互連線,支持有源和無源元件,并提供非常可靠的密封封裝解決方案,具有廣泛的好處,包括防止潮濕,熱,熱膨脹,機械沖擊和腐蝕等。 陶瓷多層基板也有利于在層壓板內實現嵌入式電感和電容器,因此在給定的設計中可以減少表面安裝組件的數量。 共燒陶瓷的兩種主要類型是低溫共燒陶瓷(LTCCs,low temperature co-fired ceramics)和高溫共燒陶瓷(HTCCs, high temperature co-fired ceramics)。 兩種類型的燒結的溫度的區別大約是900○ 用于LTCC和1500○為HTCC。 與HTCC相比,LTCC所需的較低溫度是由于事實上LT CC有較高的玻璃含量,使得能在較低的溫度上結合陶瓷晶粒。 LTCC也被稱為玻璃陶瓷,因為除了少量的結合劑外,玻璃還與特定成分的氧化鋁混合,以產生均勻的化合物。 LTCC和HTCC都是為了構造一個與金屬共燒的多層陶瓷基板而制造的。 在金屬化方面,LTCC在低于金屬熔點的溫度下使用高導電材料的金屬組成,如銅、金或銀。 然而,HTCC使用電阻率相對較高的金屬,如鎢、鉬或鉬錳,在高溫下共燒,以支持機械剛性和長期可靠性非常重要的應用。

在LTCC或HTCC中,多層基組分的生產首先通過鑄造陶瓷復合材料來產生均勻厚度的金屬片。 然后,金屬片被圖案化,并根據給定設計的布局使用沖床來創建孔洞。 然后,三維(3D)結構是由二維(2D)片構成的,其中通孔填充通常使用厚膜絲網印刷工藝。 陶瓷多層襯底的制備在加工順序上不同于半導體襯底。 在半導體制造中,層被依次加工在彼此的頂部;而在陶瓷制造過程中,每一層被單獨圖案化,然后堆疊和共燒,以建立均勻的多層結構。

LTCC和HTCC技術的關鍵區別包括:

● 與HTCC相比,LTCC具有較低的介電常數和較低的損耗

● HTCC具有較高的溫度和機械穩定性

● LTCC具有較高的金屬導電性

● LTCC層數較高;

● LTCC制造周期較短;

● LTCC使用相對低成本的工具。

采用低成本阻燃4(FR4,flame retardant 4)材料的PCB基板是由玻璃增強環氧樹脂制成的,適用于低頻應用。 FR4介質材料的損耗角正切是限制其高頻應用的一個限制因素。 其他PCB基板,如羅杰斯(Rogers)的層壓板,提供低損耗材料,可使用高達20GHz,合理的插入損耗。 柔性和有機多氯聯苯也是可用的,它們的使用主要與可穿戴醫療設備以及機器人等輕量級移動設備有關。 陶瓷基板在具有較低的熱膨脹系數方面優于PCB基板,可以在較高的溫度下工作,能夠實現密封封裝,提供更好的熱性能、更好的高頻性能,并通過在多層基板中嵌入無源元件以實現較小的封裝尺寸來實現高的集成密度。

下面的討論在一定程度上強調了不同的半導體襯底技術,這些技術主要與RFICs和MICs的制造相關。 半導體襯底材料分為元素半導體和化合物半導體兩大類:.

● 單元素半導體,在元素周期表的IV族中發現,如硅(Si)。

● 化合物半導體可進一步分為三個亞類:.

– 二元素化合物由III-V族元素(如GaAs和AlP)和II-VI組元素(如ZnS)組成。

– 三元素化合物由III-V族元素形成,如InGaAs和AlGaAs等。

– 四元素化合物由III族和V族中的四個元素組成,如InGaAsP。

由于傳統的Si光刻工藝的成熟,Si晶圓基板是半導體制造中用于實現大多數RFICs的主要材料。 另一種在特定應用中獲得牽引力的襯底材料是砷化鎵(GaAs),它在MMIC中的應用更為突出。 GaAs是一種半絕緣襯底,其元件具有較低的電容損耗和導體損耗。GaAs被開發并用于集成電路制造,以克服Si基板器件在高頻使用時遇到的工作頻率限制。 與Si相比,GaAs材料的高電子遷移率使GaAs在高速電路中處于有利地位。 然而,高昂的制造成本限制了其經濟可行性。 硅鍺(SiGe) 是將Si制造的加工成熟度、集成水平和成本效益與GaAs等更昂貴技術的速度和性能相結合的另一種半導體技術。 與Si技術制造的晶體管相比,SiGe基晶體管的電流、噪聲和功率能力有了顯著的提高。 SiGe非常適合需要高頻工作(GHz頻率范圍)和高速通信電路(如數據轉換器)的應用領域。 預計未來幾年,SiGe的市場份額將增加,特別是隨著5G網絡的部署和對大規模互聯網連接的需求。 然而,目前,SiGe正面臨來自替代技術的高度競爭。

純硅基板是一種低電阻材料,對塊體Si基器件的金屬結構造成介質損耗。 因此,在Si襯底上實現的無源組件比在GaAs襯底上實現的無源組件具有更低的Q值。對低功耗微電子技術的需要推動了幾種晶圓襯底技術的發展,以在塊體Si襯底和器件金屬層之間實現絕緣,如藍寶石上的硅(SOS,silicon on sapphire)和絕緣體上的硅(SOI, silicon on insulator)。

SOS是20世紀60年代發展起來的一種晶圓基板技術,是生產高速低功耗器件的途徑。 其中SOS的主要優點之一是具有優良的線性性能,這是大功率RFFE(射頻前端)模塊的關鍵要求。 然而,SOS的可制造性是一個限制因素,因為形成具有最小結晶缺陷的Si層主要困難阻礙了大批量生產的潛力,因此也阻礙了SOS器件產品商業化的潛力。 美國公司Peregrine半導體公司最近的發展極大地改善了藍寶石晶片上Si薄膜的結晶特性,為RFIC器件制造商今后可能采用和考慮鋪平了道路。 本質上,SOS襯底是利用外延生長在藍寶石襯底上沉積Si膜而產生的。 反過來,這將產生結晶缺陷,因為晶格不匹配藍寶石。 這一缺陷是通過在Si膜內植入Si離子來消除Si膜在與藍寶石襯底的界面上的結晶效應,并將其轉化為非晶態條件。 在熱處理和氧化環境下,Si膜被再結晶形成。然后去除剩余的SiO2 薄膜以獲得所需的SOS襯底。

SOI襯底的基本結構是在頂部薄Si層和塊體Si襯底之間形成SiO2 層,而器件是建立在其中的。 在芯片制造中,SOI晶片襯底技術被認為是一個進化的步驟,與SOS等其他技術相比具有幾個優勢。 主要優點是器件金屬層與襯底之間的寄生電容降低;因此,可以獲得更好的電氣性能。 例如,SOI襯底通常用于制造射頻開關的基于場效應的晶體管(FETs)減少源和漏到襯底的電容,而這反過來又對開關隔離、速度和插入損耗產生顯著影響。 此外,SOI襯底技術在溫度上的性能變化較小,與大多數傳統的制造工藝兼容,不需要特殊的培訓和設備來制造。

最常見的SOI晶片的制造工藝是通過注入氧(SIMOX,separation by implantation of oxygen)進行分離,形成塊狀硅支撐晶圓之上的電絕緣SiO2 層。 其他應用使用通過注入氮氣(SIMNI,implantation of nitrogen)進行分離,其中氧氣被氮氣或氧氣和氮氣(SIMON)的組合所取代,而不產生任何不利影響。所有的SIMOX、SIMNI和SIMON工藝都有很好的能力精確控制氧化層的厚度。 氧或氮離子被離子束注入硅中。 離子束的能量決定了絕緣層的深度以及后續硅覆蓋層的厚度。

雖然SOI技術正在成為IC行業面臨的幾個技術挑戰的答案,但超薄SOI層的生產以建立器件的體Si與掩埋氧化物層之間的低輪廓以及厚度均勻性仍然是一個突出的挑戰。 此外,由于氧化層的熱導率低(SiO2 為0.4W/m-K,如果與純塊狀Si相比(Si為150W/m-K)),SOI可能會受到自熱效應的影響。