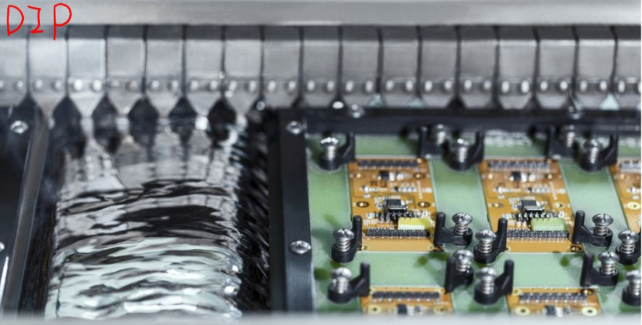

1、DIP

DIP是20世紀(jì)70年代出現(xiàn)的封裝形式。它能適應(yīng)當(dāng)時(shí)多數(shù)集成電路工作頻率的要求,制造成本較低,較易實(shí)現(xiàn)封裝自動(dòng)化印測(cè)試自動(dòng)化,因而在相當(dāng)一段時(shí)間內(nèi)在集成電路封裝中占有主導(dǎo)地位。但DIP的引腳節(jié)距較大(為2.54mm),并占用PCB板較多的空間,為此出現(xiàn)了SHDIP和SKDIP等改進(jìn)形式,它們?cè)跍p小引腳節(jié)距和縮小體積方面作了不少改進(jìn),但DIP最大引腳數(shù)難以提高(最大引腳數(shù)為64條)且采用通孔插入方式,因而使它的應(yīng)用受到很大限制。

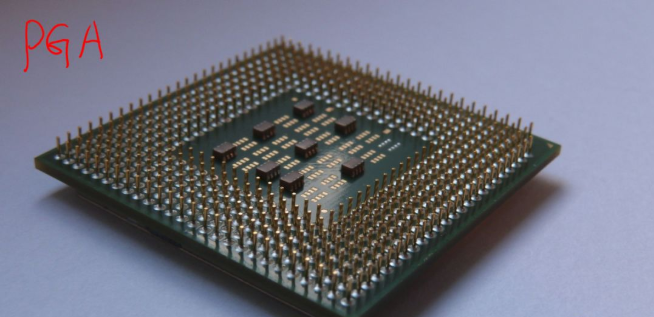

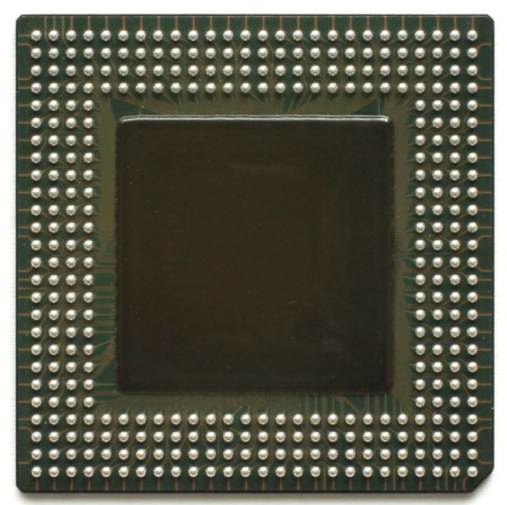

2、PGA

為突破引腳數(shù)的限制,20世紀(jì)80年代開(kāi)發(fā)了PGA封裝,雖然它的引腳節(jié)距仍維持在2.54mm或1.77mm,但由于采用底面引出方式,因而引腳數(shù)可高達(dá)500條~600條。

3、SOP

隨著表面安裝技術(shù) (surfacemounted technology, SMT)的出現(xiàn),DIP封裝的數(shù)量逐漸下降,表面安裝技術(shù)可節(jié)省空間,提高性能,且可放置在印刷電路板的上下兩面上。 SOP應(yīng)運(yùn)而生,它的引腳從兩邊引出,且為扁平封裝,引腳可直接焊接在PCB板上,也不再需要插座。它的引腳節(jié)距也從DIP的2.54mm減小到1.77mm。后來(lái)有SSOP和TSOP改進(jìn)型的出現(xiàn),但引腳數(shù)仍受到限制。

4、QFP

QFP也是扁平封裝,但它們的引腳是從四邊引出,且為水平直線,其電感較小,可工作在較高頻率。引腳節(jié)距進(jìn)一步降低到1.00mm,以至0.65mm和0.5 mm,引腳數(shù)可達(dá)500條,因而這種封裝形式受到廣泛歡迎。但在管腳數(shù)要求不高的情況下,SOP以及它的變形SOJ(J型引腳)仍是優(yōu)先選用的封裝形式,也是目前生產(chǎn)最多的一種封裝形式。

方形扁平封裝-QFP (Quad Flat Package)

[特點(diǎn)] 引腳間距較小及細(xì),常用于大規(guī)模或超大規(guī)模集成電路封裝。必須采用SMT(表面安裝技術(shù))進(jìn)行焊接。操作方便,可靠性高。芯片面積與封裝面積的比值較大。

小型外框封裝-SOP (Small Outline Package)

[特點(diǎn)] 適用于SMT安裝布線,寄生參數(shù)減小,高頻應(yīng)用,可靠性較高。引腳離芯片較遠(yuǎn),成品率增加且成本較低。芯片面積與封裝面積比值約為1:8。

據(jù)統(tǒng)計(jì),DIP在封裝總量中所占份額為15%,SOP在封裝總量中所占57%, QFP則占12%。預(yù)計(jì)今后DIP的份額會(huì)進(jìn)一步下降,SOP也會(huì)有所下降,而QFP會(huì)維持原有份額,三者的總和仍占總封裝量的80%。

以上三種封裝形式又有塑料包封和陶瓷包封之分。塑料包封是在引線鍵合后用環(huán)氧樹(shù)脂鑄塑而成,環(huán)氧樹(shù)脂的耐濕性好,成本也低,所以在上述封裝中占有主導(dǎo)地位。陶瓷封裝具有氣密性高的特點(diǎn),但成本較高,在對(duì)散熱性能、電特性有較高要求時(shí),或者用于國(guó)防軍事需求時(shí),常采用陶瓷包封。

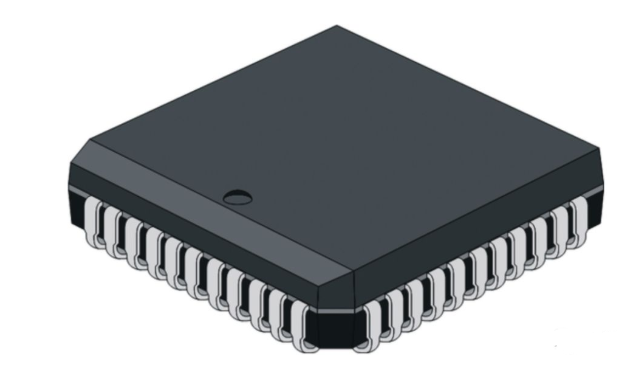

5、PLCC

PLCC是一種塑料有引腳(實(shí)際為J形引腳)的片式載體封裝(也稱四邊扁平J形引腳封裝QFJ(quad flat J-lead package)),所以采用片式載體是因?yàn)橛袝r(shí)在系統(tǒng)中需要更換集成電路,因而先將芯片封裝在一種載體(carrier)內(nèi),然后將載體插入插座內(nèi),載體和插座通過(guò)硬接觸而導(dǎo)通的。這樣在需要時(shí),只要在插座上取下載體就可方便地更換另一載體。

6、TAB

TAB封裝技術(shù)是先在銅箔上涂覆一層聚酰亞胺層。然后用刻蝕方法將銅箔腐蝕出所需的引腳框架;再在聚酰亞胺層和銅層上制作出小孔,將金屬填入銅圖形的小孔內(nèi),制作出凸點(diǎn)(采用銅、金或鎳等材料)。由這些凸點(diǎn)與芯片上的壓焊塊連接起來(lái),再由鑄塑技術(shù)加以包封。它的優(yōu)點(diǎn)是由于不存在內(nèi)引線高度問(wèn)題.因而封裝厚度很薄,此外可獲得很小的引腳節(jié)距(如0.5mm,0.25mm)而有1000個(gè)以上的引腳等,但它的成本較高,因而其應(yīng)用受到限制。

7、BGA球柵陣列封裝

球柵陣列(Ball Grid Array)封裝是在封裝體基板的底部制作陣列,焊球作為電路的I/O端與印刷線路板(PCB)互接,采用該項(xiàng)技術(shù)封裝的器件是一種表面貼裝型器件。此技術(shù)常用來(lái)永久固定如微處理器之類的的裝置。BGA封裝能提供比其他如雙列直插封裝(Dual in-line package)或四側(cè)引腳扁平封裝(Quad Flat Package)所容納更多的接腳,整個(gè)裝置的底部表面可全作為接腳使用,而不是只有周圍可使用,比起周圍限定的封裝類型還能具有更短的平均導(dǎo)線長(zhǎng)度,以具備更佳的高速效能

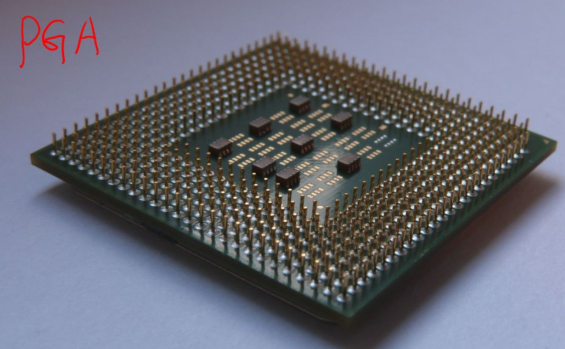

8、PGA插針網(wǎng)格陣列封裝

PGA (Pin Grid Array Package)芯片封裝形式在芯片的內(nèi)外有多個(gè)方陣形的插針,每個(gè)方陣形插針沿芯片的四周間隔一定距離排列。根據(jù)引腳數(shù)目的多少,可以圍成2-5圈。安裝時(shí),將芯片插入專門的PGA插座。為使CPU能夠更方便地安裝和拆卸,從486芯片開(kāi)始,出現(xiàn)一種名為ZIF的CPU插座,專門用來(lái)滿足PGA封裝的CPU在安裝和拆卸上的要求。ZIF(ZeroInsertion Force Socket)是指零插拔力的插座。把這種插座上的扳手輕輕抬起,CPU就可很容易、輕松地插入插座中。然后將扳手壓回原處,利用插座本身的特殊結(jié)構(gòu)生成的擠壓力,將CPU的引腳與插座牢牢地接觸,絕對(duì)不存在接觸不良的問(wèn)題。而拆卸CPU芯片只需將插座的扳手輕輕抬起,則壓力解除,CPU芯片即可輕松取出。 PGA封裝具有以下特點(diǎn): 1.插拔操作更方便,可靠性高。2.可適應(yīng)更高的頻率。

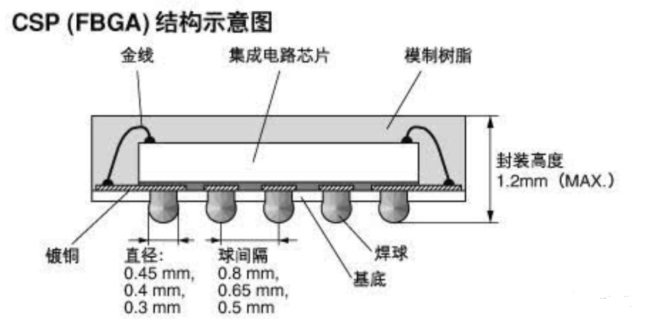

9、芯片尺寸封裝CSP

芯片尺寸封裝CSP(Chip Size Package)是近年來(lái)發(fā)展起來(lái)的一種新封裝技術(shù)。它減小了芯片封裝外形的尺寸,做到裸芯片尺寸有多大,封裝尺寸就有多大。 CSP的定義為:封裝周長(zhǎng)等于或小于芯片裸片周長(zhǎng)的1.2倍,或者封裝面積小于裸片面積的1.5倍。因而CSP的封裝效率(指硅片面積與封裝后的總面積之比)比QFP和BGA都要高。CSP有一些不同的結(jié)構(gòu),如撓性基板的插入式、陶瓷剛性基板的插入式、面陣列凸焊點(diǎn)式和片上引腳式(1eadon chip)等。如LOC,它與以往的封裝結(jié)構(gòu)不同,它不再將芯片先粘接在基板上,面是直接粘接在引腳框架上(即取消基板),這樣可縮小封裝側(cè)面到芯片之間的距離(可縮小到0.4mm~0.5mm)。