隨著信息技術的發展,圖像傳感器越來越多的應用在科學研究和生產生活中,目前使用的主要是CCD圖像傳感器和CMOS圖像傳感器。其中以CCD為采集數據源的圖像采集技術取得了長足的進步,作為高性能的光電圖像傳感器以其優良的性能廣泛應用于遙感成像、高精測量、景物鑒別、圖文傳真和工業檢測控制等領域。本文提出了一種實時圖像采集和處理系統的設計方法,該系統以TMS320DM642[1-2]為核心,結合視頻解碼芯片SAA7115H和OSD FPGA構成實時圖像采集和處理系統電路。

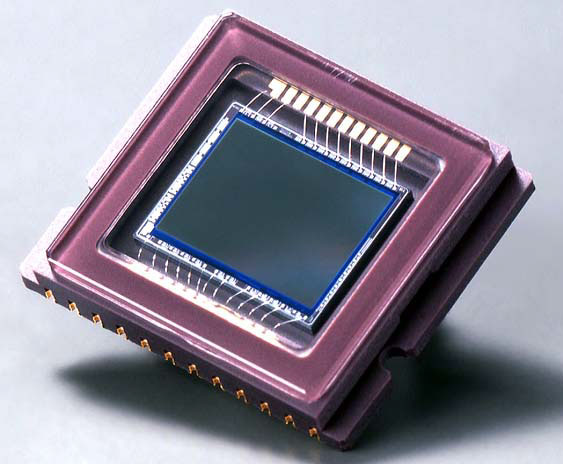

CCD,英文全稱:Charge-coupled Device,中文全稱:電荷耦合元件。可以稱為CCD圖像傳感器。CCD是一種半導體器件,能夠把光學影像轉化為數字信號。 CCD上植入的微小光敏物質稱作像素(Pixel)。一塊CCD上包含的像素數越多,其提供的畫面分辨率也就越高。CCD的作用就像膠片一樣,但它是把圖像像素轉換成數字信號。CCD上有許多排列整齊的電容,能感應光線,并將影像轉變成數字信號。經由外部電路的控制,每個小電容能將其所帶的電荷轉給它相鄰的電容。

1 系統總體設計

1.1 系統結構

本系統以TMS320DM642為核心,采用模塊化設計思想,整個系統主要由視頻解碼芯片(A/D轉換芯片)、可編程邏輯門陣列(OSD FPGA)、TMS320DM642及外圍電路組成。外圍電路主要包括CCD攝像機、SDRAM圖像存儲器、FLASH程序存儲器及TMS320DM642外圍電路(復位、電源連接等)。圖1為該系統的結構框圖。

1.2 系統工作原理

由CCD攝像頭攝入的PAL制圖像傳送到SAA7115解碼器,SAA7115解碼?E5%r?99?將信號轉變成并行的BT.656圖像碼流送至TMS320DM642視頻口VP0,TMS320DM642將其再解碼,得到YUV(4:2:2)格式的圖像,并通過EDMA傳輸到動態存貯器(SDRAM)中存儲,圖像大小為每場720×288(寬×高),每幀720×576(寬×高)。CPU通過訪問SDRAM中的圖像數據,依照相應的程序進行相應的圖像處理。

在實時圖像處理系統中,為了不影響數據處理速度,需要在恒速的CCD圖像采集與變速的TMS320DM642圖像處理之間加入緩沖電路,緩沖采用TMS320DM642視頻口的片內FIFO和片外SDRAM的乒乓緩存結構。"乒乓操作"是一個經常應用于數據流控制的處理方法,如圖2所示,其處理流程為:輸入數據流通過指針等時地將數據流分配到數據緩沖區1、2和3中,在第1幀的時間,將輸入的數據流緩存到1;第2幀將輸入的數據流緩存到2,與此同時,將1的數據作運算處理。在下個緩沖周期,再次切換,將輸入的數據流緩存到3,與此同時,將2的數據運算處理。如此循環,A、B、C、D、E為其5種狀態。

乒乓操作的最大特點是按節拍、相互配合地切換,將經過緩沖的數據流不停頓地進行運算及處理。把乒乓操作模塊當作一個整體,此模塊兩端的輸入數據流與輸出數據流均是連續不斷的,沒有任何停頓,因此非常適合進行流水線式處理,完成數據的無縫緩沖與處理。

2 功能模塊設計

2.1 視頻采集模塊

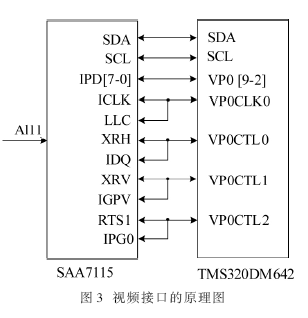

本系統采用Philips公司的SAA7115視頻解碼芯片將CCD模擬視頻進行數字化,然后傳給TMS320DM642的視頻端口進行處理,同時分離水平同步(XRH)和垂直同步(XRV)等信號。

視頻解碼芯片采用SAA7115,省去時鐘同步電路的設計,簡化接口電路,提高系統的可靠性。由攝像機采集到的模擬信號經過視頻端子進入到解碼器SAA7115的模擬端Al11,經模擬處理和A/D轉換后產生數字色度信號和亮度信號,分別對其進行處理。亮度信號處理的結果一路送到信號處理器,進行綜合處理,產生Y和UV信號,經格式化后采用4:2:2 YUV格式從IPD[7-0]輸出直接連接到TMS320DM642視頻口的VP0[9-2]管腳;另一路經過同步分離器,由數字PLL產生相應的同步信號與TMS320DM642的VP0CTL0和VP0CTL1相連,同時PLL驅動時鐘發生器,產生27 MHz的時鐘同步信號LLC,輸出到TMS320DM642的VP0CLK0管腳。解碼器SAA7115與TMS320DM642的視頻接口的原理如圖3所示。

所有這些功能均在I2C總線控制下完成。SCL作為I2C接口的時鐘線與TMS320DM642的SCL相連,SDA作為I2C接口的數據地址線與TMS320DM642的SDA相連。通過SCL和SDA的時序配合,可由TMS320DM642向SAA7115的寄存器寫入數據或讀出數據。

2.2 TMS320DM642圖像處理模塊

本系統中視頻口VP0作為輸入,與視頻解碼器SAA7115的IPD相連。從解碼器SAA7115出來的BT.656數據流進入VP0口后,經由BT.656捕獲通道,進入到視頻口緩沖區中,每個視頻口都有1個5 120 B的視頻輸入/輸出緩沖區,視頻口輸人的數據分別進入捕獲FIFO A和FIFO B,其中Y緩存2 560 B,Cb和Cr緩存分別為1 280 B.根據輸出的同步脈沖產生幀存儲器的地址信號、讀寫和片選等控制信號,將圖像逐幀存入SDRAM存儲器中,通過中斷通知TMS320DM642讀取。TMS320DM642通過EDMA事件實現視頻口緩沖區和片內L2存儲器之間的數據傳遞。用戶編程設定1個緩沖區閾值用以產生EDMA事件。BT.656格式的數據流經由捕獲通道分別進入各自的緩沖區,并打包成64 B的雙字。當雙字增至緩沖區閾值時觸發EDMA事件,存儲器映射寄存器即作為EDMA數據傳輸的源地址。為保證每一場的數據能夠全部傳完且沒有遺漏,每次EDMA傳輸的數據大小應等于閾值。由于TMS320DM642的強大處理能力,用戶算法作為任務線程嵌入TMS320DM642軟件系統中。

2.3 外圍存儲模塊

本系統的TMS320DM642在視頻圖像的處理時,處理過程中會產生大量數據,而其內部最多僅有256 KB的RAM,所以需要擴展大容量的外部存儲器才能滿足數據處理的需要。本系統選用2片SDRAM用于存儲程序、數據和緩存數字視頻信息,選用1片FLASH存儲器用于固化程序和一些掉電后仍需保存的用戶數據。SDRAM芯片和FLASH芯片均通過TMS320DM642的EMIF口實現無縫連接[3].TMS320DM642的EMIF有4個獨立的可設定地址的區域,稱為芯片使能空間(CE0~CE3),當FLASH和FPGA映射到CE1時,SDRAM占據CE0,CE3的一部分被配置給OSD功能的同步操作和擴展的FPGA中的其他同步寄存器操作。本系統合并形成了一個64 bit長的外部存儲器端口,將地址空間分割成了4個芯片使能區,允許對地址空間進行8 bit、16 bit、32 bit和64 bit的同步或不同步的存取,并且使用了芯片使能區CE0、CE1和CE3.CE0被發送給64 bit的SDRAM總線,CE1被8 bit的FLASH和FPGA功能使用,CE3被設置成同步功能。

2.3.1 SDRAM存儲器

SDRAM:Synchronous Dynamic Random Access Memory,同步動態隨機存儲器,同步是指 Memory工作需要同步時鐘,內部的命令的發送與數據的傳輸都以它為基準;動態是指存儲陣列需要不斷的刷新來保證數據不丟失;隨機是指數據不是線性依次存儲,而是自由指定地址進行數據讀寫。

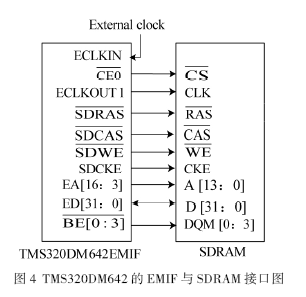

本系統采用MT48LC4M32B2[4]來構成SDRAM存儲器,大小為1 M×32 bit×4 banks, 在CE0空間連接了64 bit的SDRAM總線。總線由外部PLL驅動設備控制,在133MHz的最佳運行狀態下運行,SDRAM的刷新由TMS320DM642自動控制。TMS320DM642的EMIF與SDRAM接口圖如圖4所示。

2.3.2 FLASH存儲器

FLASH閃存 閃存的英文名稱是"Flash Memory",一般簡稱為"Flash",它屬于內存器件的一種。 不過閃存的物理特性與常見的內存有根本性的差異: 目前各類 DDR 、 SDRAM 或者 RDRAM 都屬于揮發性內存,只要停止電流供應內存中的數據便無法保持,因此每次電腦開機都需要把數據重新載入內存。

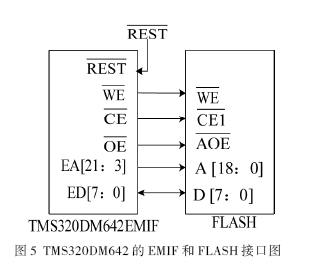

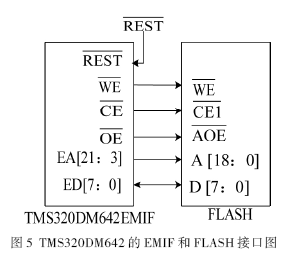

本系統擴展4 M的FLASH,映射在CE1空間的低位。FLASH寄存器選用4 M×8 bit的AM29LV033C.FLASH寄存器主要用來導入裝載和存儲FPGA的配置信息。CE1空間被配置成8 bit,FLASH寄存器也是8bit.由于CE1的可利用地址空間小于FLASH的空間,所以利用FPGA可產生3個擴展頁。這些擴展的線形地址通過FPGA的FLASH基礎寄存器進行定義,復位后的默認值是000.TMS320DM642的EMIF和FLASH的接口圖如圖5所示。

2.4 OSD FPGA模塊

OSD是on-screen display的簡稱,即屏幕菜單式調節方式。一般是按Menu鍵后屏幕彈出的顯示器各項調節項目信息的矩形菜單,可通過該菜單對顯示器各項工作指標包括色彩、模式、幾何形狀等進行調整,從而達到最佳的使用狀態。它通過顯示在屏幕上的功能菜單達到調整各項參數的目的,不但調整方便,而且調整的內容也比以上的兩種方式多,增加了失真、會聚、色溫、消磁等高級調整內容。像以前顯示器出現的網紋干擾、屏幕視窗不正、磁化等需要送維修廠商維修的故障,現在舉手之間便可解決。

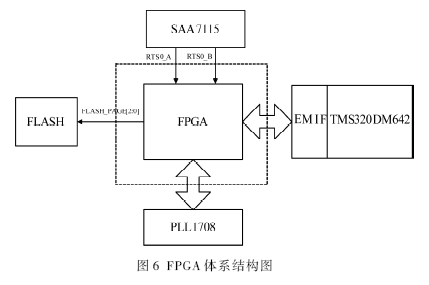

FPGA負責完成所有芯片的接口和控制,其中包括SAA7115與I2C總線的接口、復位控制信號以及與TMS320DM642的EMIF接口和外設接口等,其體系結構圖如圖6所示。本系統的OSD FPGA功能模塊的芯片型號為Xilinx XC2S300E-6PQ208C[5],主要用來完成以下工作:

(1)通過寄存器使用TMS320DM642外部存儲器接口(EMIF);

(2)通過可編譯寄存器使用TMS320DM642的EMIF接口控制GPIO;

(3)產生EMIF緩沖控制信號(DIR和OE);

(4)提供對于PLL1708的連續控制接口;

(5)為FLASH產生3頁bit空間;

(6)使用SAA7115的同步信號。

2.5 電源和復位模塊

該系統通過單+5 V供電,在板子內部轉換為+1.4 V和+3.3 V,為各器件供電。+3.3 V為TMS320DM642的I/O口、解碼器及其他芯片的電源,+1.4 V為TMS320DM642 CPU內核電源。TMS320DM642內核電壓+1.4 V,外設I/O電壓+3.3 V,降低內核電壓主要是降低功耗,外部接口引腳采用+3.3 V電壓,便于直接與外部器件接口。由于是2種不同的電壓,所以要考慮供電系統的配合問題。在加電過程中,保證CPU內核電源先加電,最晚也應當與外設I/O電源同時加電。關閉電源時,先關閉I/O電源,再關閉內核電源。如果內核加電晚于I/O,則會發生內部總線競爭,從而產生不可預定的結果。因此,選用電源芯片TPS54310[6]獲得上述2種電壓,并利用其電源輸出有效引腳PG和允許電壓輸人引腳EN保證TMS320DM642的內核和I/O上電掉電順序。

為防止系統程序進入死循環或因電壓波動而產生異常,本系統用看門狗芯片來控制系統復位。這里采用TI的TPS3823-33DBVT[7]看門狗芯片,它由+3.3 V電源供電,能對電源電壓進行監控,當電源電壓降至2.93 V以下時觸發復位信號,使整個系統進入復位狀態,直至電源電壓復原,復位信號的最小長度為200 ms.同時,還含有一看門狗計時器,用來監測來自處理器芯片的跳變沿觸發信號,如果1.6 s內未接收到觸發信號,它同樣讓系統進入復位狀態并持續200 ms,這樣可在系統程序進入死循環后重新啟動系統。TMS320DM642電源與復位電路的連接圖如圖7所示。

3 抗干擾設計

由于高頻脈沖噪聲對本系統危害最大,為了提高系統的抗干擾性能,可采取以下措施:

(1)優化PCB印制板的設計。在本系統中應當:

①采用短而寬的導線來抑制干擾。時鐘引線、總線驅動器的信號線常有大的瞬變電流,其印制導線要盡可能短。對于分立元件電路,印制導線寬度在1.5 mm左右即可滿足要求;對于集成電路,印制導線寬度在0.5 mm~1.0 mm之間選擇;

②傳輸多種電平信號時,盡量把前、后沿時間相近的電平信號劃為一組傳輸;在雙面印制板的背面布置較大面積的地線區域,可對部件產生的高頻脈沖噪聲起到吸收和屏蔽的作用;分開模擬和數字電源層;

(2)增加總線的抗干擾能力。采用三態門形式的總線結構,并給總線接上拉電阻,使總線在瞬間處于穩定的高電平而避免總線出現懸空狀態。

本文面向實時圖像采集和處理,采用模塊化設計思想,以TMS320DM642、SAA7115、OSD FPGA等實現了視頻圖像采集和處理系統的硬件電路,該系統電路簡單、結構緊湊、調節靈活、可靠性高、實時性強的特點,通過驗證,滿足設計的應用要求,可為今后視頻圖像采集和處理的進一步研發提供參考。